DUDLEY KNUX LIBAARY NAVAL POSPORADUATE SCHOOL MONTEREY, CALIFORNIA 05945-5002

## NAVAL POSTGRADUATE SCHOOL Monterey, California

## THESIS

A SERIAL BUS ARCHITECTURE FOR PARALLEL PROCESSING SYSTEMS

by

Kevin J. Delaney

September 1986

Thesis Advisor:

Larry W. Abbott

T230328

Approved for public release; distribution is unlimited.

# NUMBER OF TAXABLE

v

### -1-21/1

,

12111

SECURITY CLASSIFICATION OF THIS PAGE

|                                                               |                                                                                |                                                     |                                                                         | REPORT DOCU                                                                                                                              | MENTATION                                                                            | PAGE                                                                |                               |                                               |                                                   |

|---------------------------------------------------------------|--------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------|-----------------------------------------------|---------------------------------------------------|

| 1a REPORT S<br>UNCLA                                          | SSIFIED                                                                        | SIFICATI                                            | ON                                                                      |                                                                                                                                          | 1b. RESTRICTIVE                                                                      | MARKINGS                                                            |                               |                                               |                                                   |

| 2a SECURITY                                                   | CLASSIFICATIO                                                                  | N AUT                                               | HORITY                                                                  |                                                                                                                                          |                                                                                      | AVAILABILITY OF                                                     |                               | -                                             |                                                   |

| 26 DECLASSI                                                   | FICATION / DOV                                                                 | WNGRA                                               | DING SCHEDU                                                             | LE                                                                                                                                       |                                                                                      | d for publ<br>ution is u                                            |                               |                                               |                                                   |

| 4 PERFORMI                                                    | NG ORGANIZA1                                                                   | TION RE                                             | PORT NUMBE                                                              | R(S)                                                                                                                                     | 5 MONITORING                                                                         | ORGANIZATION RE                                                     | PORT                          | NUMBER(S                                      | )                                                 |

| 6a. NAME OF                                                   | PERFORMING                                                                     | ORGAN                                               | IZATION                                                                 | 66 OFFICE SYMBOL                                                                                                                         | 7a. NAME OF MO                                                                       | DNITORING ORGAN                                                     | IZAT                          | ION                                           |                                                   |

| Naval                                                         | Postgrad                                                                       | luate                                               | e School                                                                | (If applicable)<br>62                                                                                                                    | Naval Po                                                                             | ostgraduat                                                          | e S                           | chool                                         |                                                   |

| 6c. ADDRESS                                                   | (City, State, an                                                               | d ZIP C                                             | ode)                                                                    |                                                                                                                                          | 76. ADDRESS (Cit                                                                     | y, State, and ZIP Co                                                | ode)                          |                                               |                                                   |

| Monte                                                         | rey, Cal                                                                       | ifoi                                                | rnia 93                                                                 | 8943-5000                                                                                                                                | Montere                                                                              | y, Califor                                                          | nia                           | 9 39 4                                        | 3-5000                                            |

| Ba NAME OF<br>ORGANIZA                                        | FUNDING/SPO                                                                    | NSORI                                               | IG                                                                      | 8b OFFICE SYMBOL<br>(If applicable)                                                                                                      | 9. PROCUREMENT                                                                       | INSTRUMENT IDEI                                                     | NTIFI                         | CATION NUI                                    | MBER                                              |

| Bc. ADDRESS (                                                 | City, State, and                                                               | I ZIP CO                                            | de)                                                                     |                                                                                                                                          | 10 SOURCE OF F                                                                       | UNDING NUMBERS                                                      |                               |                                               |                                                   |

|                                                               |                                                                                |                                                     |                                                                         |                                                                                                                                          | PROGRAM<br>ELEMENT NO                                                                | PROJECT<br>NO                                                       | task<br>NO                    |                                               | WORK UNIT<br>ACCESSION NO                         |

| A SER                                                         | AUTHOR(S)                                                                      | ARCH                                                | ITECTUR                                                                 | E FOR PARALL                                                                                                                             | EL PROCESSI                                                                          | ING SYSTEM                                                          | S                             |                                               |                                                   |

| 3a TYPE OF<br>Master's                                        | REPORT<br>5 Thesi                                                              | s                                                   | 135 TIME CO<br>FROM                                                     | VERED<br>TO                                                                                                                              | 14 DATE OF REPO<br>1986 Sept                                                         | RT (Year, Month, D.<br>Lember                                       | ay)                           | 15 PAGE (<br>64                               | COUNT                                             |

| 6 SUPPLEME                                                    | NTARY NOTAT                                                                    | ION                                                 |                                                                         |                                                                                                                                          |                                                                                      |                                                                     |                               |                                               |                                                   |

| 7                                                             | COSATI                                                                         | CODES                                               |                                                                         | 18 SUBJECT TERMS (                                                                                                                       | Continue on reverse                                                                  | if necessary and                                                    | ident                         | ify by block                                  | number)                                           |

| FIELD                                                         | GROUP                                                                          | SUE                                                 | 3-GROUP                                                                 | Parallel p                                                                                                                               | rocessing,                                                                           | Optoelect                                                           | ron                           | ic Mul                                        | tiplexer                                          |

| 9 ABSTRACT                                                    | (Continue on i                                                                 | reverse                                             | if necessary                                                            | and identify by block i                                                                                                                  | number)                                                                              |                                                                     |                               |                                               |                                                   |

| process<br>munica<br>two co<br>The<br>chip.<br>the da<br>more | sor arch<br>tion bet<br>ommunica<br>e first<br>The wid<br>ata tran<br>communic | itec<br>ween<br>tion<br>con<br>er t<br>sfer<br>atio | tures h<br>the di<br>s-based<br>straint<br>he comm<br>. As I<br>n capac | ous deterran<br>as been the<br>screte proce<br>constraints<br>is related<br>unication pa<br>ntegrated Ci<br>ity is neede<br>ing technolo | problem of<br>ssing eleme<br>to the phys<br>th the more<br>rcuits grow<br>d, pushing | providing<br>ents. This<br>sical struc<br>e pins are<br>v in comput | ad<br>5 p<br>ctu<br>ne<br>tat | equate<br>aper e<br>re of<br>eded to<br>ional | com-<br>xamines<br>the VLSI<br>o effect<br>power, |

The second constraint, somewhat related to the first, is the limited speed with which data can be transmitted via internal channels. Typical speeds one can achieve on a single wire are on the order of 1 Gbps. The

| 0 DISTRIBUTION / AVAILABILITY OF AB                  | ME AS RPT DTIC USERS                                       | 21 ABSTRACT SECURITY CLASSIFICA<br>UNCLASSIFIED   | TION                       |

|------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------|----------------------------|

| 23 NAME OF RESPONSIBLE INDIVIDUA<br>Abbott, Larry W. |                                                            | 22b TELEPHONE (Include Area Code)<br>408-646-2379 | 22c OFFICE SYMBOL<br>62At  |

| D FORM 1473, 84 MAR                                  | B3 APR edition may be used un<br>All other editions are ob | SECURITY                                          | LASSIFICATION OF THIS PAGE |

#### 19. (continued)

recent development of an Optoelectronic Multiplexer may allow VLSI chips to communicate at rates up to 7 Gbps. An architecture for a parallel processing computer which takes advantage of this new capability is presented. The feasibility of a single-chip parallel processor based on the Optoelectronic Multiplexer is examined by projecting current trends in processor speed, power, and transistor count into estimates of throughput for a multi-processor IC. Approved for public release; distribution is unlimited.

A Serial Bus Architecture for Parallel Processing Systems

by

Kevin J. Delaney Lieutenant, United States Navy B.S.E.E., United States Naval Academy, 1979

Submitted in partial fulfillment of the requirements for the degrees of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING and ELECTRICAL ENGINEER

from the

NAVAL POSTGRADUATE SCHOOL September 1986

#### ABSTRACT

One of the most serious deterrants to the development of multiple processor architectures has been the problem of providing adequate communication between the discrete processing elements. This paper examines two communications-based constraints.

The first constraint is related to the physical structure of the VLSI chip. The wider the communication path the more pins are needed to effect the data transfer. As Integrated Circuits grow in computational power, more communication capacity is needed, pushing designs closer to the pin limitations of the packaging technology.

The second constraint, somewhat related to the first, is the limited speed with which data can be transmitted via internal channels. Typical speeds one can achieve on a single wire are on the order of 1 Gbps. The recent development of an Optoelectronic Multiplexer may allow VLSI chips to communicate at rates up to 7 Gbps. An architecture for a parallel processing computer which takes advantage of this new capability is presented. The feasibility of a single-chip parallel-processor based on the Optoelectronic Multiplexer is examined by projecting current trends in processor speed, power, and transistor count into estimates of throughput for a multi-processor IC.

#### TABLE OF CONTENTS

| I.   | INT       | <b>FRODUCTION</b> 10                             |

|------|-----------|--------------------------------------------------|

|      | А.        | THE NEED FOR PARALLEL PROCESSING                 |

|      | В.        | PARALLEL PROCESSORS DEPEND ON<br>Communication   |

|      |           | 1. Exhaustive Communications 11                  |

|      |           | 2. Limited Communications                        |

|      | C.        | THE OPTOELECTRONIC MULTIPLEXER CONCEPT 13        |

|      |           | 1. Optical Switching Yields High Speed           |

|      |           | 2. A Suitable Architecture Sought 14             |

| II.  | OP<br>CIR | TIMUM ARCHITECTURE OF LARGE INTEGRATED<br>RCUITS |

|      | А.        | PARTIONING SILICON FOR MAXIMUM<br>THOUGHPUT      |

|      |           | 1. Transistor Constraints   18                   |

|      |           | 2. Power Constraints                             |

|      | В.        | MINIMUM CHIP SIZE FOR OM APPLICATION             |

|      |           | 1. Minimum Transistor Count                      |

|      |           | 2. Minimum Power Dissipation                     |

| III. | TH        | E NEED FOR A HIGH-SPEED MULTIPLEXER              |

|      | А.        | PROCESSOR POWER LIMITED BY<br>COMMUNICATION PATH |

| IV.  | SYS<br>CO | STEM ARCHITECTURE BASED ON SERIAL 37             |

|      | A.        | ON-CHIP DATA FLOW ARCHITECTURE                   |

|      |           | 1. Pipeline Architecture                         |

|      |           | 2. Reuse Architecture                            |

|      |           | 3. Interleaving Data Sets                        |

|      | В.        | DATA DISTRIBUTION                                |

|      |           | 1. Pipeline Architecture                         |

|         |      | 2. Reuse Architecture                           |

|---------|------|-------------------------------------------------|

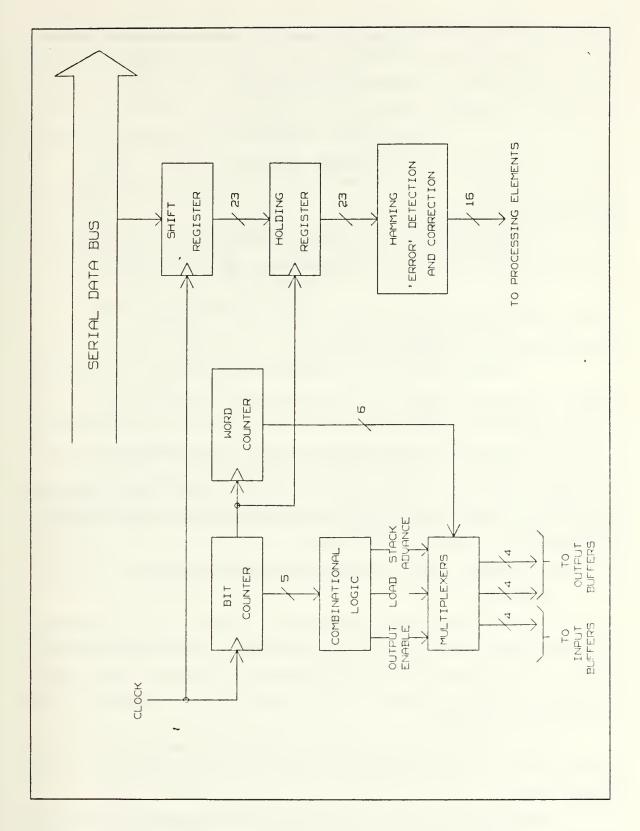

|         | C.   | RECEIVER TASKS                                  |

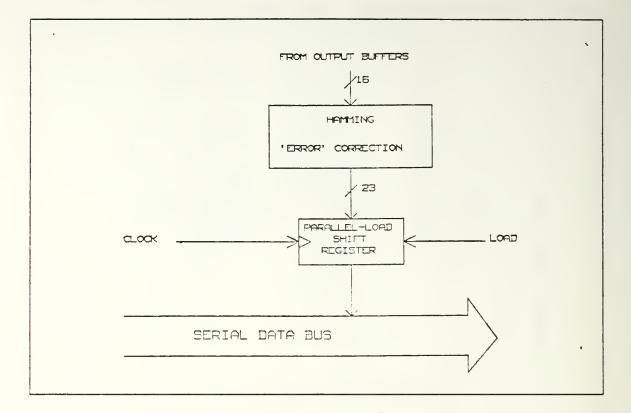

|         | D.   | TRANSMITTER TASKS                               |

|         | E.   | CONCLUSIONS AND LIMITATIONS OF THIS<br>RESEARCH |

|         |      | 1. Conclusions                                  |

|         |      | 2. Limitations and Recommendations              |

| LIST OF | REFE | ERENCES                                         |

| INITIAL | DIST | TRIBUTION LIST    63                            |

#### LIST OF TABLES

| Ι.    | SPECIFICATIONS OF SOME ACTUAL PROCESSORS 18                         |

|-------|---------------------------------------------------------------------|

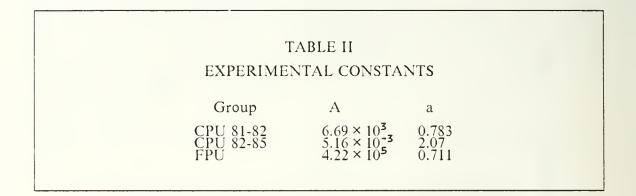

| II.   | EXPERIMENTAL CONSTANTS                                              |

| III.  | SPECIFICATIONS OF SOME ACTUAL PROCESSORS                            |

| IV.   | EXPERIMENTAL CONSTANTS                                              |

| V.    | INTER-PROCESSOR COMMUNICATIONS 4 X 1 REUSE<br>ARCHITECTURE          |

| VI.   | INTER-PROCESSOR COMMUNICATIONS 2 X 2 REUSE<br>ARCHITECTURE          |

| VII.  | INTER-PROCESSOR COMMUNICATIONS MODIFIED 4 X 1<br>REUSE ARCHITECTURE |

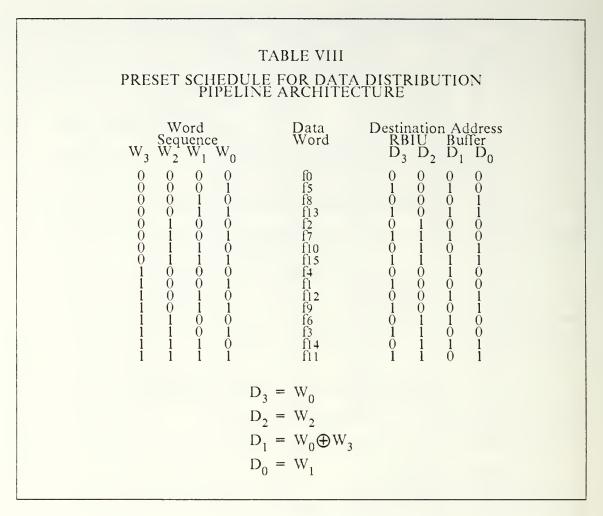

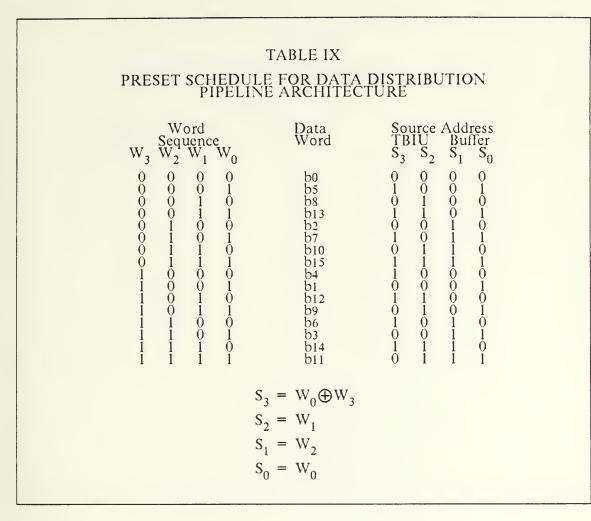

| VIII. | PRESET SCHEDULE FOR DATA DISTRIBUTION PIPELINE<br>ARCHITECTURE      |

| IX.   | PRESET SCHEDULE FOR DATA DISTRIBUTION PIPELINE ARCHITECTURE         |

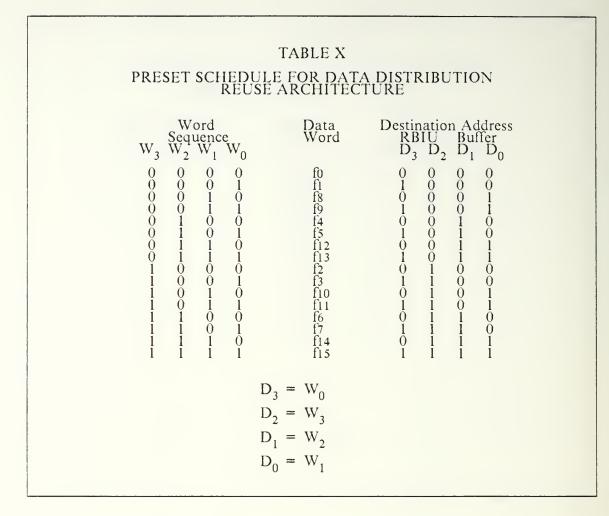

| Х.    | PRESET SCHEDULE FOR DATA DISTRIBUTION REUSE<br>ARCHITECTURE         |

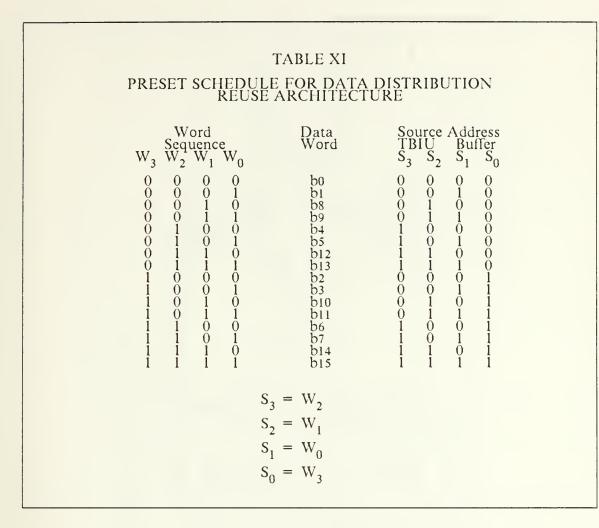

| XI.   | PRESET SCHEDULE FOR DATA DISTRIBUTION REUSE<br>ARCHITECTURE         |

#### LIST OF FIGURES

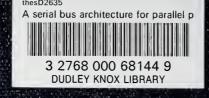

| 1.1  | Exhaustive Communicatons                                                                                     |

|------|--------------------------------------------------------------------------------------------------------------|

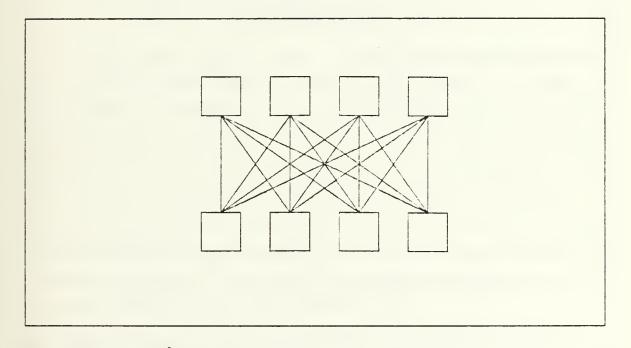

| 1.2  | Limited CommunicationsDedicated Path Loop                                                                    |

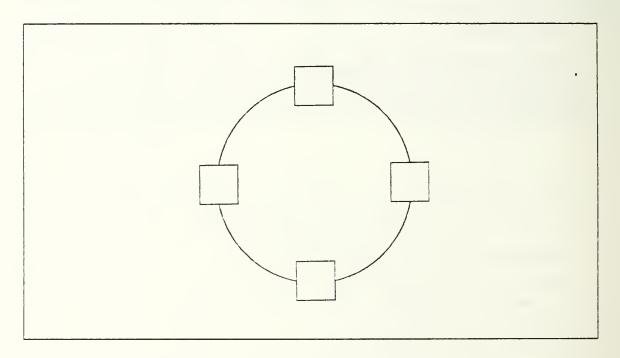

| 1.3  | Limited CommunicationsDedicated Path Regular Network                                                         |

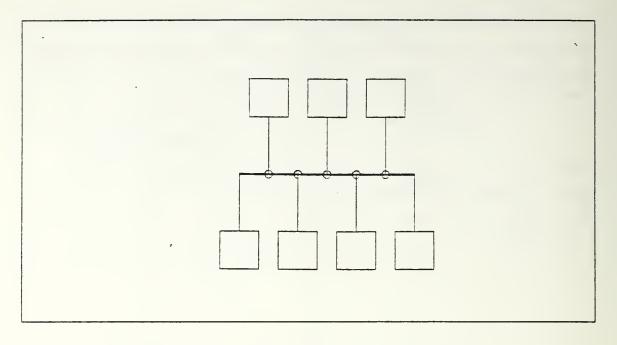

| 1.4  | Limited CommunicationsShared Path 14                                                                         |

| 1.5  | Optoelectronic Multiplexer Block Diagram 15                                                                  |

| 2.1  | Processor Speed and Complexity (Experimental) 19                                                             |

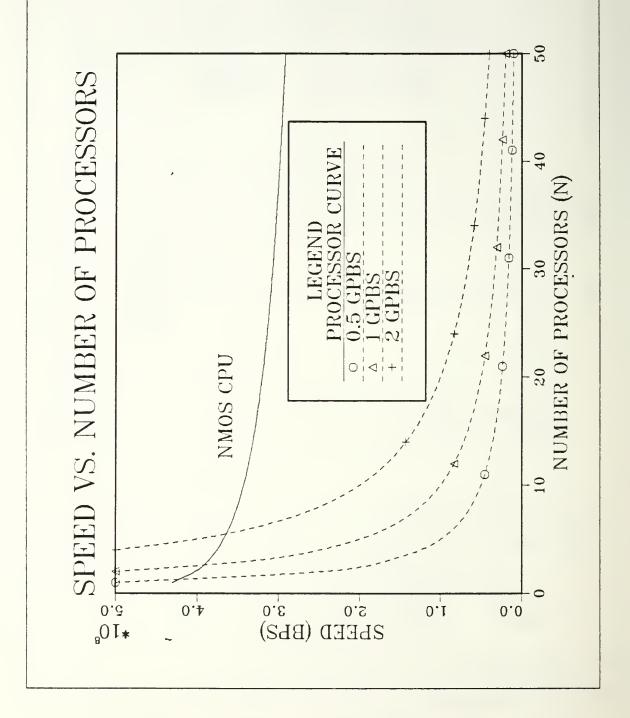

| 2.2  | Processor Speed and Number of Processors Based on a Constant<br>Number of Transistors                        |

| 2.3  | Relationship Between Processor Capability And System<br>Requirements (Speed a Strong Function of Complexity) |

| 2.4  | Relationship Between Processor Capability And System<br>Requirements (Speed a Weak Function of Complexity)   |

| 2.5  | Processor Speed and Power (Experimental)                                                                     |

| 2.6  | Processor Speed and Number of Processors Based on a Constant<br>Chip Power Level                             |

| 2.7  | Relationship Between Processor Capability And System<br>Requirements (Speed a Weak Function of Power)        |

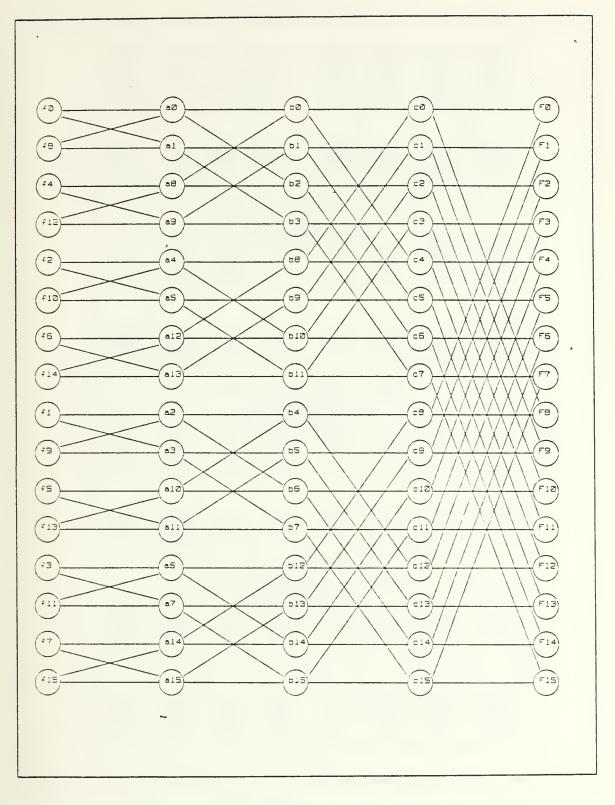

| 4.1  | Sixteen Point Fast Fourier Transform                                                                         |

| 4.2  | Sixteen Point Fast Fourier Transform Pipline Implementation                                                  |

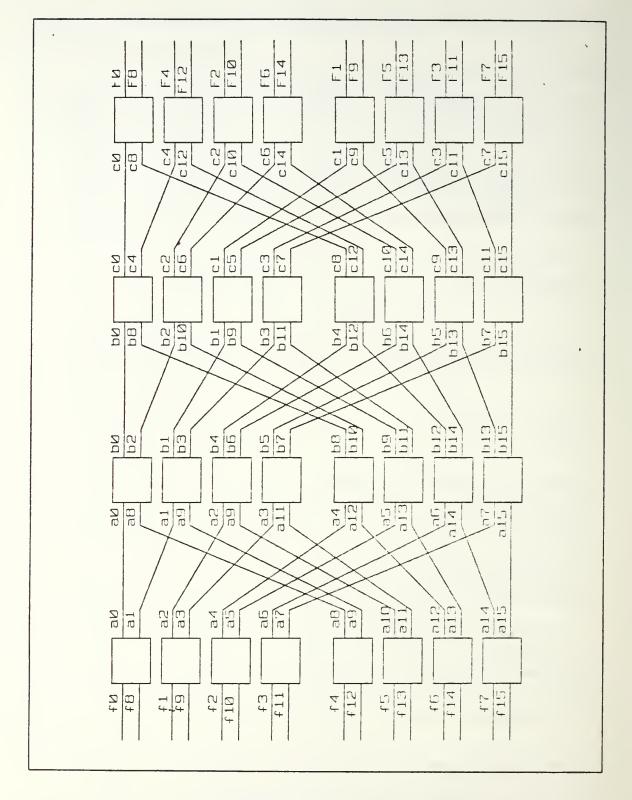

| 4.3  | Sixteen Point Fast Fourier Transform Performed by $4 \times 1$ Chips 41                                      |

| 4.4  | Sixteen Point Fast Fourier Transform Performed by $2 \times 2$ Chips 42                                      |

| 4.5  | Sixteen Point Fast Fourier Transform $4 \times 1$ Reuse Architecture                                         |

| 4.6  | Sixteen Point Fast Fourier Transform 2 × 2 Reuse Architecture                                                |

| 4.7  | Sixteen Point Fast Fourier Transform Modified 4 × 1 Reuse<br>Architecture                                    |

| 4.8  | Sixteen Point Fast Fourier Transform Modified 4 × 1 Reuse<br>Architecture Non-Interleaved                    |

| 4.9  | Sixteen Point Fast Fourier Transform Modified 4 × 1 Reuse<br>Architecture Interleaved                        |

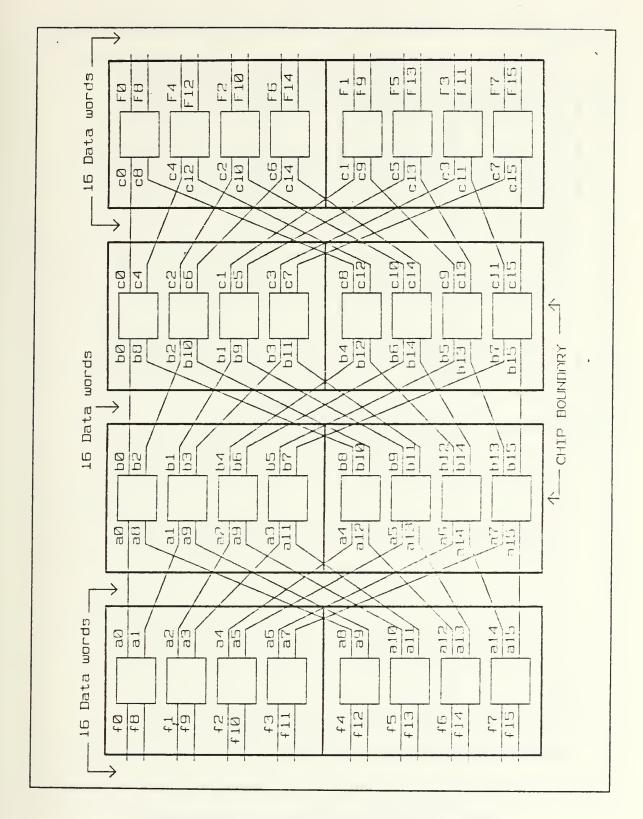

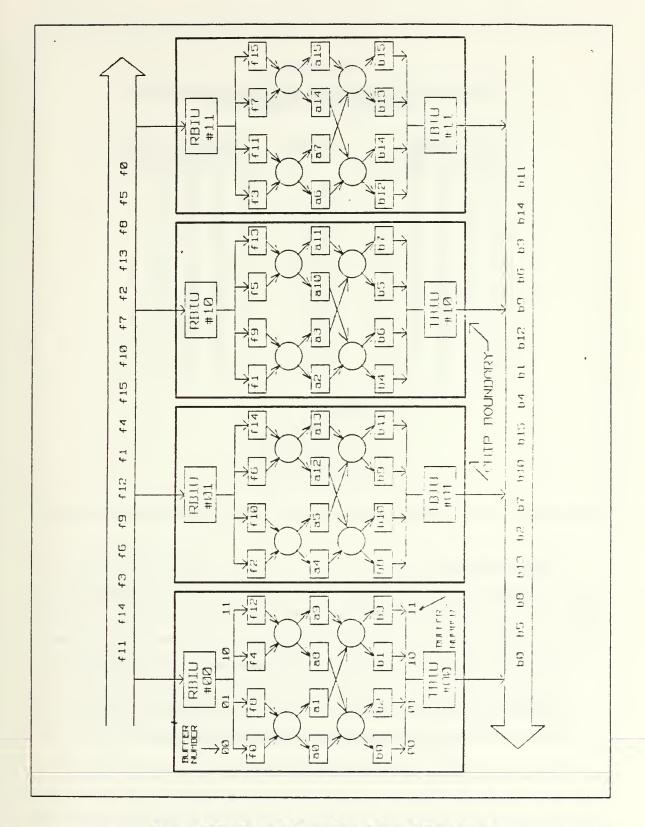

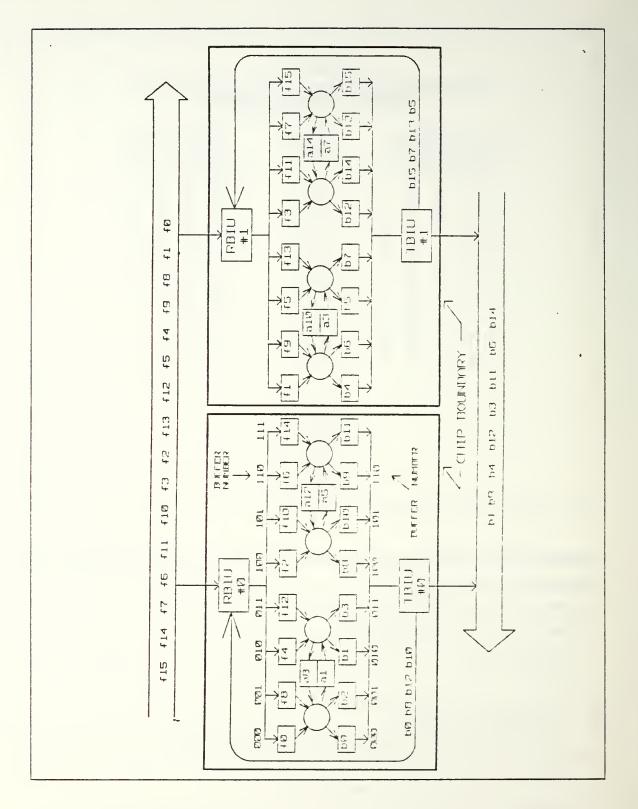

| 4.10 | Sixteen Point Fast Fourier Transform Distributed Among Four<br>Multi-Processor Chips                         |

| 4.11 | Sixteen Point Fast Fourier Transform Distributed Between Two<br>Chips Using a Reuse Architecture             |

| 4.12 | Receiving Bus Interface Unit Architecture    | 57 |

|------|----------------------------------------------|----|

| 4.13 | Transmitting Bus Interface Unit Architecture | 58 |

#### I. INTRODUCTION

Farmers once used oxen to plow their fields. And when the task got too big for one ox they did *not* try to grow a bigger ox. They got *two* of them! [Ref. 1]

#### A. THE NEED FOR PARALLEL PROCESSING

So too have we often found that one computer is not enough, or at least, not *fast* enough for many applications. While progress on producing faster single processor computers continues, it is the orders of magnitude leap in speed possible in multiple-processor computers that promises to lead computing into its Fifth Generation.

[Multiple-processor computers became] necessary because a limit to higher speed had been reached with brute-force approaches employing faster switching devices. Faster components made with gallium arsenide or Josephson junction devices can increase computer speed only 10 times if current uniprocessor architectures are used; however with the new architectures, there is hope of increasing speed 100 to 1000 times. [Ref. 2]

Such dramatic increases in computer speed would be of great benefit to researchers working on computationally-intensive and/or real time problems such as adaptive antenna control, weather prediction, or fusion reactor design. It is not merely a question of having the answers in seconds instead of minutes--once machines can perform calculations in *real time*, whole new applications suddenly become possible.

As an example, consider a computer system which calculates the power spectral density of intercepted radar emitters. A system which takes an hour to analyze a few seconds' worth of data may be useful to compile electronic intelligence data back at fleet headquarters--it produces answers long after the event is over. However, if the system could perform its analysis in real time it could be used onboard ship or in an aircraft to recognize hostile missile seekers and dispense chaff or activate jammers--that is, to respond to events as they happen. Increased speed alone could make this new application possible.

#### B. PARALLEL PROCESSORS DEPEND ON COMMUNICATION

When using a number of processors on a single problem, the exchange of data between processors becomes a critical bottleneck. [Ref. 3]

Extensive research has already been conducted in many areas related to parallel processing, such as task distribution and software development. The research reported in this paper focused on the architecture of parallel-processing systems, especially with regard to inter-processor communications.

A system which uses more than one processor to perform a task must provide communication paths between the processors. There are essentially two approaches to this requirement:

- provide a path from every processor to every other processor--"exhaustive" communications

- provide paths between each processor and only some of the other processors--"limited" communications.

Figure 1.1 Exhaustive Communicatons.

#### 1. Exhaustive Communications

An exhaustive communication architecture (Figure 1.1) provides direct data exchange without bus contention or waiting. However, as the number of processors rises, the number of communication paths in an exhaustive architecture becomes impractically large, leading to high costs. In addition, expansion of the network may be limited by the inability of the existing processors to accept another communication port. These difficulties with exhaustive communciation architectures have led many researchers to consider architectures based on limited communications.

#### 2. Limited Communications

In limited communication architectures, [Ref. 4] identifies two major groups: dedicated path and shared path structures. Limited architectures employing dedicated paths enable a processor to exchange data without bus contention or waiting, but only with a limited number, of processors. Figures 1.2 and 1.3 show two examples of a limited communication architecture employing dedicated paths.

Figure 1.2 Limited Communications--Dedicated Path Loop.

Parallel-computing systems built around a limited communications-dedicated path concept can take advantage of the immediate communication between a given processor and the processors adjacent to it. Yet if a problem requires communication between non-adjacent processors, the message must be passed along by all the intermediate processors. Should the message reach a busy node, it may be delayed or even discarded, forcing a re-transmission. The resultant communication overhead could tie up the system and severely slow its operation.

Figure 1.3 Limited Communications--Dedicated Path Regular Network.

Using a shared path (as in Figure 1.4) eliminates the need to relay data from one processor to another, because an uninterrupted path already exists between any two processors. For this reason, limited shared-path architectures are more flexible in the kinds of data flows which can be achieved and in the types of problems which can be solved than limited dedicated-path architectures. However, because processors must wait their turn to use the common communication path, system throughput may suffer. That is, unless the common bus runs at such a high speed that the processors can barely keep up with the bus. Such a high speed bus design would require a multiplexer on each chip capable of speeds considerably in excess of the speeds associated with conventional multiplexers. The Optoelectronic Multiplexer (OM) developed by the Naval Ocean Systems Center, San Diego, is such a device.

#### C. THE OPTOELECTRONIC MULTIPLEXER CONCEPT

#### 1. Optical Switching Yields High Speed

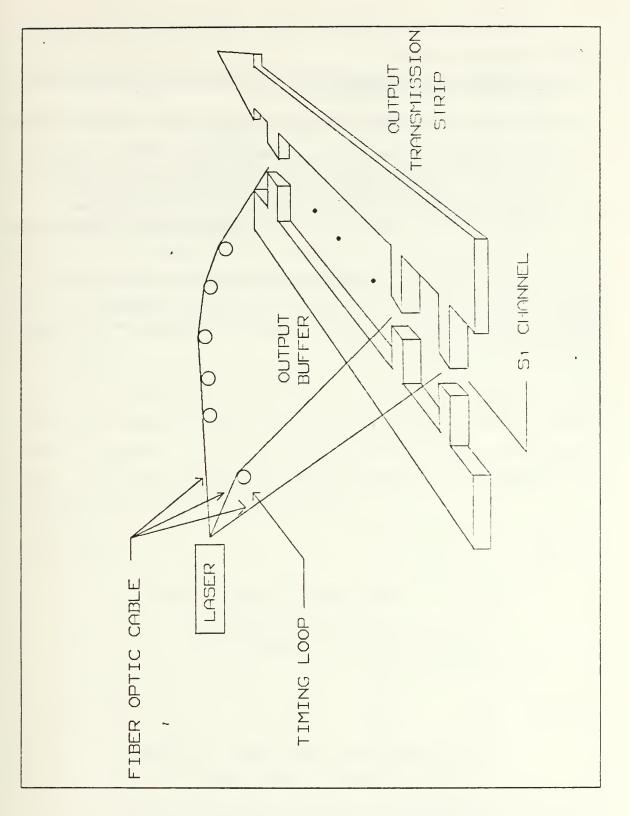

The Optoelectronic Multiplexer employs optically-activated junctions to sequentially link parallel data lines onto a serial bus. [Ref. 5] A laser pulse, fed to the junction by optical fiber, activates the junction, allowing conduction from the input line onto the main data transmission line. By using a different length of optical fiber

Figure 1.4 Limited Communications--Shared Path.

for each junction, the laser pulses will arrive at the junctions at different times. Consequently, the junctions are activated one at a time, which converts the parallel data waiting on the input lines to serial data pulses travelling along the output transmission line. The short pulsewidths generated by the laser allow extremely high pulse repetition frequencies--researchers have tested a prototype laser multiplexer at speeds as high as 7 Gbps. [Ref. 5]

#### 2. A Suitable Architecture Sought

Current research [Refs. 6 - 10] is especially rich in parallel-processing architectures based on limited communication dedicated-path concepts, because shared path communications typically involve delays which could detract from the high performance otherwise achievable by parallel-processing designs. Prompted by the development of the high-speed Optoelectronic Multiplexer, which promises an increase in serial communication speed of at least one and perhaps two orders of magnitude, this project evaluated the impact of using a shared bus and serial communication in a parallel processing computer architecture. Specifically, the following questions were posed: With current technology, is it feasible to fabricate an Optoelectronic Multiplexer-based multiple processor chip? What new architectures are made possible by the OM's high speed? Which architecture makes optimum use of this new capability?

Figure 1.5 Optoelectronic Multiplexer Block Diagram [Ref. 11].

Four conditions would have to be met in order for a single-chip OM-based parallel processor to be feasible:

- IC manufacturing technology should be able to fabricate enough transistors on a single chip to create a multi-processor chip.

- A large chip partitioned into many processors would produce higher throughput than the same chip fabricated as a large uniprocessor.

- Chip throughput (measured in bits per second) would exceed the capacity of conventional multiplexers, justifying the use of the OM.

- The package of such a multiple processor chip would require so many pins that package size would be excessive and a multiplexer would be used instead.

The first condition is easily dealt with by a specific example. The Intel 8080 microprocessor contained about 4500 transistors [Ref. 12], while Motorola's MC68020 contains about 200000 [Ref. 13]. Using the technology of the Motorola MC68020, one could produce a chip with over 40 Intel 8080s. Clearly, manufacturers can *already* fabricate a multiple-processor chip. The remaining points require further discussion and are covered in Chapters II and III.

#### **II. OPTIMUM ARCHITECTURE OF LARGE INTEGRATED CIRCUITS**

Chapter I's demonstration that a multiple-processor chip could be fabricated prompts the following questions:

- Is a multiprocessor chip the best use of IC fabrication technology, or should all available transistors be assembled into a single processor?

- How large (in terms of transistor count, heat dissipation, and number of processors) would a chip have to be in order to justify the use of the Optoelectronic Multiplexer?

#### A. PARTIONING SILICON FOR MAXIMUM THOUGHPUT

Should designers divide the available silicon among a few large and capable processors or among many, less capable processors? Which mix yields the highest throughput?

Consider a system of N processors, each executing the same program and producing the same number of output data words each second. Applications of such architectures abound in the field of real time signal processing, which uses regularly structured algorithms. As N increases, processors share the load, so each may run more slowly without changing the speed of the *system*. If we imagine a system throughput goal of R bits per second (bps), then:

$$R = NS$$

(eqn 2.1)

where R = System throughput (bps) N = Number of processors S = Throughput of each processor (bps).

$$Sreg'd = RN^{-1}$$

(eqn 2.2)

These equations describe what is *required* of a processor--but how does a processor's *actual* performance vary with N? At issue is the apportionment of the entire chip's allotment of transistors and heat dissipation ability among N processors.

#### 1. Transistor Constraints

Assuming we can put only so many devices on a chip, then:

$$t = TN^{-1}$$

(eqn 2.3)

where t = complexity of any processor, measured in transistors N = number of processors

T = Total number of transistors on chip

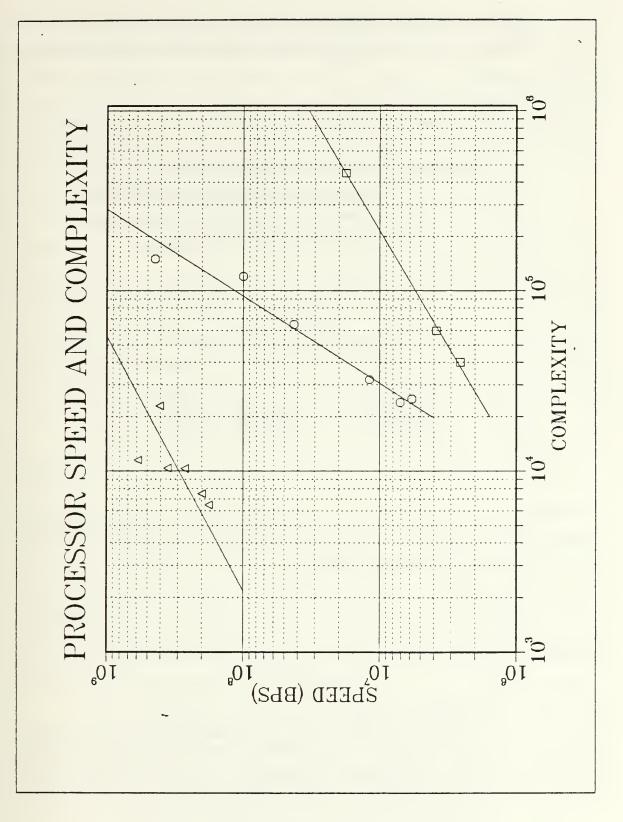

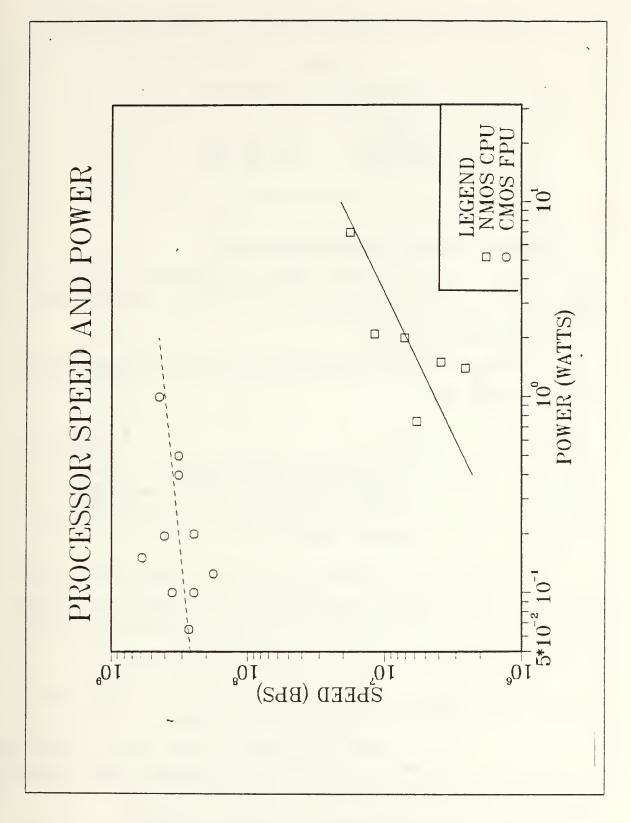

Generally, a complex processor will be able to perform a given calculation faster than a simple processor. For example, a microprocessor with an on-board floating-point unit can handle a multiplication in a few clock cycles, while a smaller processor has to do tedious successive additions, requiring much more time. But what is the exact relationship between processor complexity and speed? To answer this we shall examine the specifications of some existing processors, as listed in Table I and graphed in Figure 2.1.

|                  |                                                                | ·                                      | TABLE I                                                                                                                      |                                              |                                                                            |

|------------------|----------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------|

|                  | SPEC1FIC                                                       | ATIONS OF                              | SOME ACTUAL PF                                                                                                               | ROCESSORS                                    |                                                                            |

| Group            | Reference                                                      | Data Word<br>(Bits)                    | Time Required for<br>Multiplication                                                                                          | Bit<br>Rate                                  | Transistor<br>Count                                                        |

|                  |                                                                |                                        | $(10^{-6} \text{ sec})$                                                                                                      | (10 <sup>6</sup> sec <sup>-1</sup> )         | (thousand                                                                  |

| CPU's<br>1981-82 | Ref. 14<br>Ref. 15<br>Ref. 16                                  | 32<br>16<br>32                         | 8.30<br>6.25<br>1.80                                                                                                         | $3.86 \\ 2.56 \\ 17.8$                       | $\begin{array}{c} 60.\\ 40.\\ 450. \end{array}$                            |

| CPU's<br>1982-85 | Ref. 17<br>Ref. 18<br>Ref. 19<br>Ref. 20<br>Ref. 21<br>Ref. 22 | 32<br>32<br>32<br>32<br>32<br>32<br>80 | 5.50<br>4.50<br>2.70<br>0.75<br>0.32<br>0.18                                                                                 | 5.82<br>7.11<br>11.9<br>42.7<br>100.<br>444. | 25.<br>24.<br>32.1<br>65.<br>120.<br>150.                                  |

| FPU's            | Ref. 23<br>Ref. 24<br>Ref. 25<br>Ref. 26<br>Ref. 27<br>Ref. 28 | 16<br>16<br>16<br>16<br>16<br>16       | $     \begin{array}{r}       .090 \\       .080 \\       .060 \\       .045 \\       .027 \\       .079 \\     \end{array} $ | 178.<br>200.<br>267.<br>356.<br>593.<br>405. | $\begin{array}{r} 6.5 \\ 7.5 \\ 10.3 \\ 10.35 \\ 11.5 \\ 23.0 \end{array}$ |

Figure 2.1 Processor Speed and Complexity (Experimental).

From the experimental relationships between processor speed and complexity shown in Figure 2.1, we can see that the data in each group are approximated by the equation:

$$S_{\text{proc}} = At^a$$

(eqn 2.4)

where Sproc = processor speed (in bps throughput) t = processor complexity (in number of transistors) A = empirical constant of proportionality given in Table II a = empirical constant given in Table II.

Equation 2.4 describes how, in some typical one-processor systems, processor speed is related to complexity. To apply these findings to a N-processor system of T transistors, we combine equations 2.3 and 2.4:

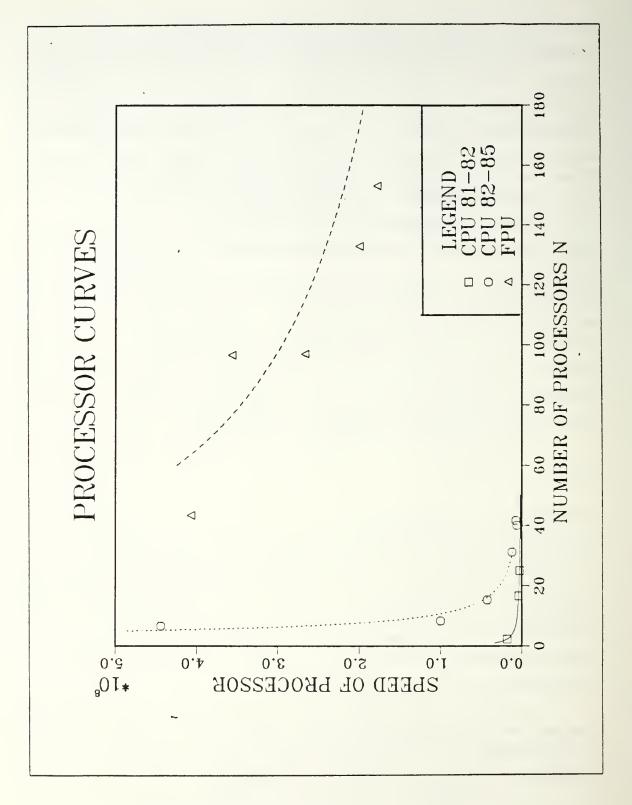

$S_{\text{proc}} = A(TN^{-1})^{a} \qquad (eqn 2.5)$   $S_{\text{proc}} = AT^{a}N^{-a}$   $S_{\text{proc}} = K_{1}N^{-a}$   $where S_{\text{proc}} = \text{processor speed (in bps throughput)}$  t = processor complexity (in number of transistors) N = number of processors A and a are constants given in Table II.

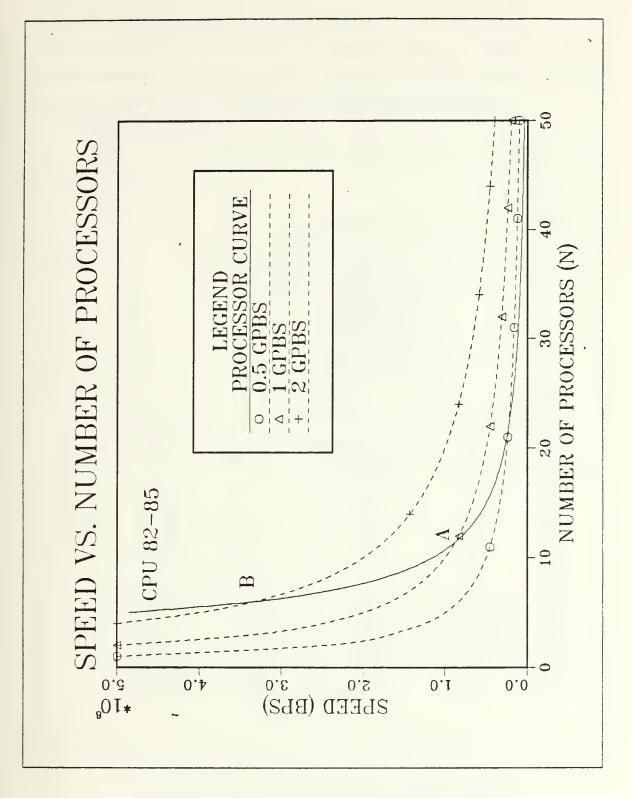

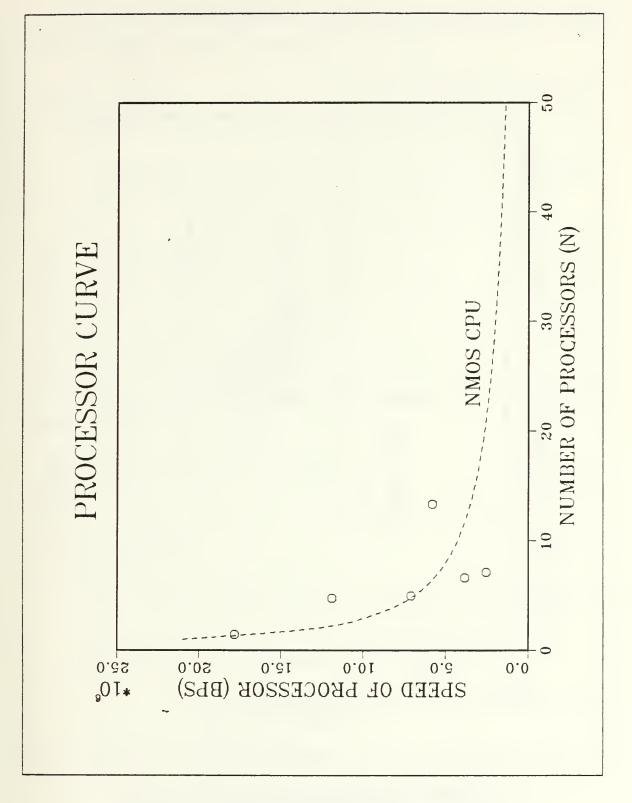

A family of "processor curves" may be used to describe the tradeoff between individual processor speed and the number of processors, constrained by a constant number of transistors. The tradeoffs are shown in Figure 2.2. For example, consider the curve labeled "CPU 82-85," which is based on a constant 10<sup>6</sup> transistors per chip. If these transistors are divided into 10 processors of  $10^5$  transistors each, Equation 2.4 predicts that each will produce about  $116 \times 10^6$  bps of output. But if the chip is divided into more (for example 25) processors of  $4 \times 10^4$  transistors each, then these less complex processors will be capable of only about  $17.3 \times 10^6$  bps each.

When we superimpose these processor curves (Figure 2.2) with a family of "system" curves, generated by choosing several values of "R" in Equation 2.2, the result (Figures 2.3 and 2.4) yields a strategy for choosing N. Where the processor curve (describing what the processor *can* do) intersects the system curve (describing what each processor *must* do) determines the number of processors (N) into which the chip should be divided to yield that particular level of system throughput. For example, to achieve a system throughput of 10<sup>9</sup> bps, Figure 2.3 shows the chip should be divided into about 12 processors (point A). Yet choosing to partition the silicon into fewer, larger processors (point B) yields a higher system throughput of 2  $\times$  10<sup>9</sup> bps.

In general, when processor speed is a *strong* function of complexity, that is when:

Sproc =

$$At^a$$

with  $a > 1$  (eqn 2.6)

then Sproc is proportional to  $N^{-a}$  (a > 1) while Sreq'd is proportional to  $N^{-1}$ . Thus, Sproc falls *faster* than Sreqd as N increases. In this case, the highest performance will always result from choosing the lowest N possible, in other words N = 1. This strategy may be constrained for very large values of T--there may not be a processor design which can effectively use 10<sup>7</sup> transistors, for example. Also, the optimistic relationship of Equation 2.6 may not hold for large values of t.

On the other hand, when a *weak* relationship exists between speed and complexity, as shown in Figure 2.4, the best strategy is to select N as *large* as possible. As before, however, there are limits to this rule. It may be impractical to divide the computational task beyond a certain point. For example, a 256-point FFT probably

Figure 2.2 Processor Speed and Number of Processors Based on a Constant Number of Transistors.

Figure 2.3 Relationship Between Processor Capability And System Requirements (Speed a Strong Function of Complexity).

Figure 2.4 Relationship Between Processor Capability And System Requirements (Speed a Weak Function of Complexity).

can not be efficiently shared by more than  $128 \ge 8 = 1024$  processors.<sup>1</sup> Also, as N increases and t decreases, processors will eventually become too simple to function as microprocessors. For example, excessive reduction in processor complexity could yield a circuit unable to retain a data word or perform a basic calculation.

#### 2. Power Constraints

Each chip can only dissipate a given amount of heat. The power available to any individual processor is:

$$p = PN^{-1}$$

(eqn 2.7)

where p = Power available to any one processor

N = number of processors

P = Total power available to the chip

|               |                                                                                                            | Ť                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                   |                                                                              |                                                                                                           |

|---------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

|               | SPECIFIC                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ABLE III<br>Some actual PF                                                                        | ROCESSORS                                                                    |                                                                                                           |

| Group         | Reference                                                                                                  | Data Word<br>(Bits)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Time Required for<br>Multiplication<br>(10° sec)                                                  | Bit<br>Rate<br>(10° sec <sup>-1</sup> )                                      | Power<br>(watts)                                                                                          |

| NMOS<br>CPU's | Ref. 14<br>Ref. 15<br>Ref. 16<br>Ref. 17<br>Ref. 18<br>Ref. 19                                             | 32<br>16<br>32<br>32<br>32<br>32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8.30<br>6.25<br>1.80<br>5.50<br>4.50<br>2.70                                                      | $\begin{array}{r} 3.86 \\ 2.56 \\ 17.8 \\ 5.82 \\ 7.11 \\ 11.85 \end{array}$ | $   \begin{array}{r}     1.50 \\     1.40 \\     7.00 \\     0.75 \\     2.00 \\     2.10   \end{array} $ |

| CMOS<br>FPU's | Ref. 23<br>Ref. 25<br>Ref. 26<br>Ref. 27<br>Ref. 28<br>Ref. 29<br>Ref. 30<br>Ref. 31<br>Ref. 32<br>Ref. 33 | $     \begin{array}{r}       16 \\       16 \\       16 \\       16 \\       32 \\       16 \\       32 \\       16 \\       32 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\       16 \\$ | $\begin{array}{c} .090\\ .060\\ .045\\ .027\\ .079\\ .100\\ .065\\ .100\\ .065\\ .130\end{array}$ | 178.<br>267.<br>356.<br>593.<br>405.<br>320.<br>246.<br>320.<br>246.<br>123. | $\begin{array}{c} 0.125\\ 0.065\\ 0.100\\ 0.15\\ 0.195\\ 0.40\\ 0.200\\ 0.500\\ 0.10\\ 0.275\end{array}$  |

<sup>&</sup>lt;sup>1</sup>There are  $256 \div 2 = 128$  processors per stage and  $\log_2(256) = 8$  stages.

Examining the relationship between processor speed and power in the light of data from actual processors, (Table III and Figure 2.5) there in no clear trend evident in Figure 2.5. In particular, there is a great deal of scatter in the CMOS multiplier chip data. This may be due to differences in the way researchers report power dissipation data; for example, some may report only the power consumption of the computational segment, while others report the power used by the entire chip, including bus drivers. In spite of these limitations, one interpretation of the power/throughput data is:

Therefore, combining equations 2.5 and 2.8 as before:

$$S_{\text{proc}} = B(PN^{-1})^{b} \qquad (eqn \ 2.9)$$

$$S_{\text{proc}} = BP^{b}N^{-b}$$

$$S_{\text{proc}} = K_{2}N^{-b}$$

where  $S_{\text{proc}} = \text{processor speed (in bps throughput)}$

$$p = \text{processor power (in watts)}$$

$$N = \text{number of processors}$$

B and b are empirical constants given in Table IV.

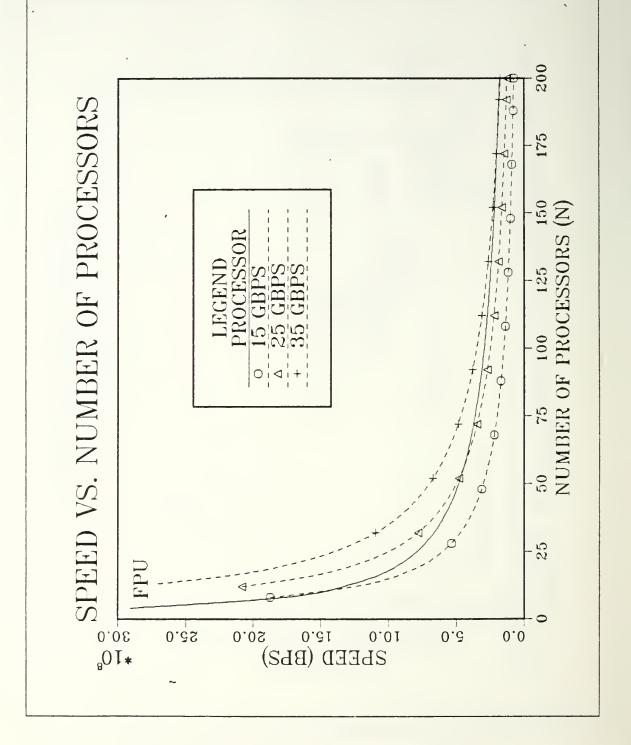

Figure 2.6 shows the relationship described in equation 2.9, namely, the tradeoff of individual processor speed against the number of processors, constrained this time by a constant power level, as required by equation 2.7. Since, for the group of actual processors examined,

$$S_{\text{proc}} = Bp^{b}$$

with  $b < 1$  (eqn 2.10)

Figure 2.7 shows that the best strategy is to select N as *large* as possible.

Figure 2.5 Processor Speed and Power (Experimental).

| TA<br>EXPERIMEN | BLE IV<br>FAL CONST    | ANTS  |

|-----------------|------------------------|-------|

| Group           | B                      | b     |

| NMOS cpu's      | 4.27 × 10 <sup>6</sup> | 0.693 |

| CMOS fpu's      | 3.43 × 10 <sup>8</sup> | 0.099 |

#### B. MINIMUM CHIP SIZE FOR OM APPLICATION

How large (in terms of transistor count, heat dissipation, and number of processors) would a chip have to be in order to produce sufficient throughput to justify the use of the Optoelectronic Multiplexer?

#### 1. Minimum Transistor Count

Assuming the individual processors are of low complexity (like the FPU group of Figure 2.1) implies that:

Sproc = At<sup>a</sup> with a < 1 (eqn 2.11) where Sproc = processor speed (in bps throughput) t = processor complexity (in number of transistors) A = empirical constant of proportionality given in Table II a = empirical constant, here < 1.

For this group, the discussion in the previous section shows that the maximum throughput is achieved by partioning the available silicon into the largest number of processors possible, limited by the minimum complexity of the simplest processor design.<sup>2</sup> Therefore:

$N_{max} = Tt_{min}^{-1}$  (eqn 2.12) where T = total number of transistors on chip  $t_{min}$  = complexity of the simplest processor design, measured in transistor

$N_{max}$  = number of simple processors possible on chip of T transistors

<sup>&</sup>lt;sup>2</sup>While the components of systolic arrays are less complex than the assumed simplest processor, this research did not study the performance of such ICs--accordingly they are not considered here.

Figure 2.6 Processor Speed and Number of Processors Based on a Constant Chip Power Level.

Figure 2.7 Relationship Between Processor Capability And System Requirements (Speed a Weak Function of Power).

Since each processor produces an output of  $S_{proc}$  bits per second and there are  $N_{max}$  processors, the system throughput is:

$$S_{sysmax} = N_{max}S_{proc}$$

(eqn 2.13)

$$= N_{max} At_{min} \qquad (eqn \ 2.14)$$

$= [Tt_{min}^{-1}]At_{min}^{a}$  (eqn 2.15)

$$= TAt_{min}^{a-1}$$

(eqn 2.16)

Defining S<sub>om</sub> to be the minimum system throughput for which use of the OM is justified leads to:

$$S_{om} = TAt_{min}^{a-1}$$

(eqn 2.17)

$$T_{\min} = S_{\min}[t_{\min}]A^{-1}$$

(eqn 2.18)

where  $t_{min}$  = minimum number of transistors on chip for OM usage to be justified

To estimate the value of T<sub>min</sub> assume:

-

t<sub>min</sub> = 4 × 10<sup>3</sup> transistors (lower end of FPU group in Table I) A = 4.22 × 10<sup>5</sup> (Table II) a = 0.711 (Table II) S<sub>om</sub> = 3 × 10<sup>9</sup> bps (Curently the upper range of conventional multiplexers.) [Refs. 34,35,36,37] Therefore:

Thus, since processors with transistor counts  $> T_{min}$  are already in existence [Ref. 21], it seems that an OM-based single chip multiple processor is feasible with respect to the number of transistors required.

## 2. Minimum Power Dissipation

What is the minimum heat dissipation of a multi-processor chip which would yield throughput in the OM range?

$$N_{max} = P p_{min}^{-1}$$

(eqn 2.19)

where P = Total power dissipation of the chip (watts)

$p_{min}$  = power used by the simplest processor design, measured in watts  $N_{max}$  = number of simple processors possible on chip of P watts

$$S_{sysmax} = N_{max}S_{proc}$$

(eqn 2.20)

Substituting from Equation 2.8,

$$S_{sysmax} = N_{max} B p_{min}^{b}$$

(eqn 2.21)

And, substituting for N<sub>max</sub> from Equation 2.19,

$$S_{sysmax} = [Pp_{min}^{-1}]Bp_{min}^{b}$$

(eqn 2.22)

$$S_{sysmax} = PBp_{min}^{b-1}$$

(eqn 2.23)

Defining  $S_{om}$  to be the minimum system throughput for which use of the OM is justified leads to:

$$S_{om} = PBp_{min}^{b-1}$$

(eqn 2.24)

$$P_{\min} = S_{\min}[p_{\min}]B^{-1}$$

(eqn 2.25)

where  $P_{min}$  = minimum power dissipation of the chip for OM usage to be justified To estimate the value of  $P_{min}$  assume:

$$p_{min} = 0.10$$

watts (lower end of CMOS FPU group in Table III)

B =  $3.43 \times 10^8$  (Table IV)

b =  $0.099$  (Table IV)

$S_{om} = 3 \times 10^9$  bps

Therefore:

$P_{min} = 1.10$  watts  $N_{max} = 11$  processors

This power level is quite reasonable, and it would seem that from the standpoint of heat dissipation an OM-based multiple processor chip is feasible.

#### **III. THE NEED FOR A HIGH-SPEED MULTIPLEXER**

Chapter II demonstrated that current technology could produce a chip whose throughput would exceed the capacity of conventional multiplexer technology. But why consider serial communications and multiplexers at all? Why not exchange data with the chip in parallel via pins or leads?

#### A. PROCESSOR POWER LIMITED BY COMMUNICATION PATH

We have seen that future high-density IC's may be optimally structured as a bank of many processors, each of moderate capability. However, even if manufacturers can achieve sufficient circuit density to fabricate a multi-processor chip, such a device might not be practical due to the large number of leads needed to communicate with each processor from off-chip. For example, imagine an N-processor IC designed to compute a 2N-point Fast Fourier Transform (FFT). During the computation, the IC must read in, then write out, 2N complex output words, or 4N real words. Assuming a 40 bit word size, and using the same pins for input and output, we can see this IC would need:

(eqn 3.1)

$$\begin{bmatrix} 40 \text{ leads} \\ \hline \text{word} \end{bmatrix} \times [4N \text{ words}] = 160N \text{ leads}$$

How large a package will we need to handle all these leads? Using a Pin-Grid Array (PGA) package with pins spaced every 0.1 inch, the area of the package is:

Area =

$$\frac{[160\text{ N leads}]}{\left[\frac{10 \text{ leads}}{25.4 \text{ mm}}\right]^2} = 1032 \text{ N mm}^2$$

(eqn 3.2)

For illustrative purposes we can estimate the area of the silicon chip in this package by assuming the chip size of the processor is approximately the same as that of the processor recently reported by the Matsushita Corporation of Osaka. [Ref. 28] Their processor performs a 32 bit floating point multiplication in about 75 nsec and is 32.6 mm<sup>2</sup> in area. A chip containing N of these processors would occupy about 32.6N mm<sup>2</sup> of silicon. Thus, the ratio of silicon area to package area in our hypothetical IC is:

Ratio of

$$\frac{\text{Silicon Area}}{\text{Package Area}} = \frac{[32.6\text{N}]}{[1032\text{N}]} = 3.2\%$$

(eqn 3.3)

As IC fabrication technology improves, this waste of space gets even worse. A new production technique enabling manufacturers to produce circuits in half the silicon area previously required would permit us to double "N" without increasing the silicon area. Yet package area *would* double, due to increased pinout requirements. Once some maximum package size is reached, further improvements in circuit density do us no good--we simply can not communicate with more processors. As one researcher stated, "the technology has become increasingly constrained by packaging limitations" [Ref. 38].

Increasing lead density will produce some relief from this communication limit, but can not be pursued beyond some maximum without excessive fabrication cost. We are faced, then, with some maximum package size and maximum lead density, implying an eventual limit on the number of leads a single IC can have.

Given this eventual limit on the number of simultaneous off-chip communication paths, Rent's Rule [Ref. 12:p. 235]

$$P = 4G^{0.6}$$

(eqn 3.4)

where  $P =$  Number of chip pads or leads

$G =$  Number of gates on the chip

would seem to imply that if the number of paths (P) is limited, then so is the number of gates (G) and, therefore microprocessor complexity and computational power.

This ultimate limit on non-multiplexed designs is not precisely defined. Neither maximum package size nor maximum lead density have yet been reached, and industry experts are wary of predicting when they might be. In addition, the switch to multiplexed designs will probably occur over a range of processor densities and complexities, influenced by market factors (there will be few customers for very large packages) and manufacturing realities (specialized chip sizes mean more expensive chip handling equipment) as well as the theoretical factors described above.

For all these reasons, large ICs composed of multiple processors will require too many pins to use a conventional parallel-transfer scheme with pins or leads. Instead a serial communications link must be considered, and as shown in Chapter II, the speeds required will exceed the capacity of conventional multiplexers.

## **IV. SYSTEM ARCHITECTURE BASED ON SERIAL COMMUNICATION**

Chapters II and III demonstrate that, in the next generation of ICs, a microprocessor may very well be organized as a bank of smaller processors, all sharing a relatively few pins through a high-speed multiplexer. But:

- What on-chip data flow architecture should be employed among these processors?

- How can a serial data stream be distributed among N processors?

- What are the detailed structures of the elements which make up an OM-based architecture?

#### A. ON-CHIP DATA FLOW ARCHITECTURE

How should a N-processor chip be organized? The ideal structure will vary with the application; this discussion considers one specific application--computing FFT's. The number of processors required to compute a given size FFT will depend on whether processors are "reused," that is whether a processor bank's outputs are shuffled and returned to the same processors (reused) or directed to the next bank of processors (pipelined). Reusing processors allows a given FFT to be computed with fewer processors, but takes more time. The architectures associated with both reuse and pipeline strategies are discussed in the following sections.

#### 1. Pipeline Architecture

Assuming that the throughput of the system is to be maximized, there will be no "reuse" of processors. That is:

- each processor performs only a two point FFT "butterfly"

- a new bank of processors performs each stage of the computation in a pipeline strategy.

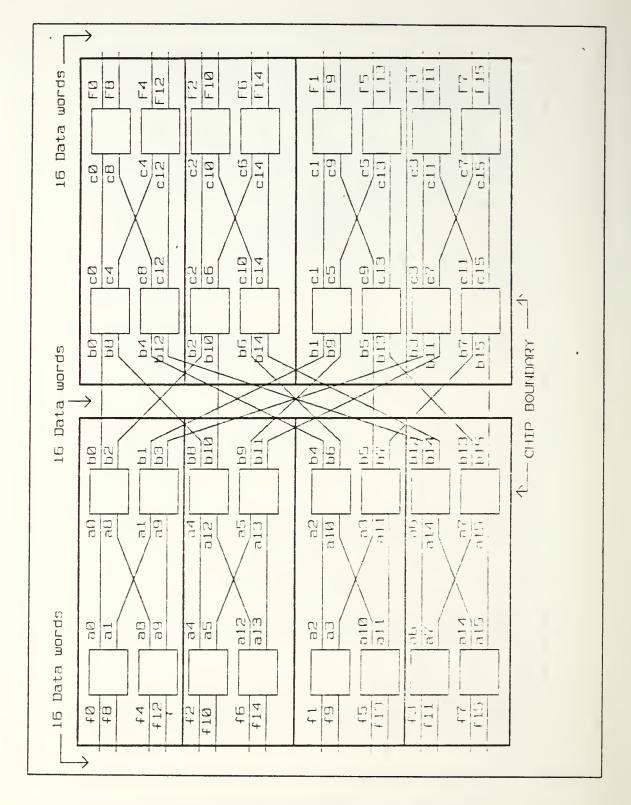

The most straightforward architecture for N processors is a N  $\times$  1 column. How would this grouping affect data flow among the processors? As an example, when the task is a 16 point FFT, the processors must exchange data as shown in Figures 4.1 and 4.2. Dividing up the 32 processors shown in Figure 4.2 into 4  $\times$  1 chips forces 80 data words to cross chip boundaries during the computation, as shown in Figure 4.3.

Re-organizing the four processors on each chip into a  $2 \times 2$  matrix (Figure 4.4) results in only 48 words crossing chip boundaries, thereby improving the system's

throughput, since off-chip communication delay is lessened, and reducing the demands on the communications network.

The 2  $\times$  2 structure is more efficient because it is the structure of a four point FFT. In a sense, the 2  $\times$  2 structure performs all the computations possible on the four points it receives, while the 4  $\times$  1 array, receiving eight points, must hand off its data only partially "chewed."

There are many such matrices, each corresponding to a particular FFT. For example, Figure 4.2 suggests that a 32 point processor IC designed for FFT computation would best be configured as a  $8 \times 4$  matrix. In general, the matrix dimensions are:

$$2^{n-1} \times n$$

where  $n = 1, 2, 3, ...$  (eqn 4.1)

#### 2. Reuse Architecture

The number of processors required by a pipeline architecture to compute a P-point FFT is:

$$P/2 \times \log_2 P$$

(eqn 4.2)

This number of processors may prove to be impractical or simply too expensive, or we may not need the ultimate throughput achievable by the pipeline architecture, yet still need more throughput than that provided by a uniprocessor. Also, it may be desirable to adapt an existing pipeline system to compute larger FFTs--without adding processors. In each of these cases, reusing processors in the computation enables the designer to tradeoff system throughput for design complexity and cost. How are data exchanged among processors in a reuse architecture?

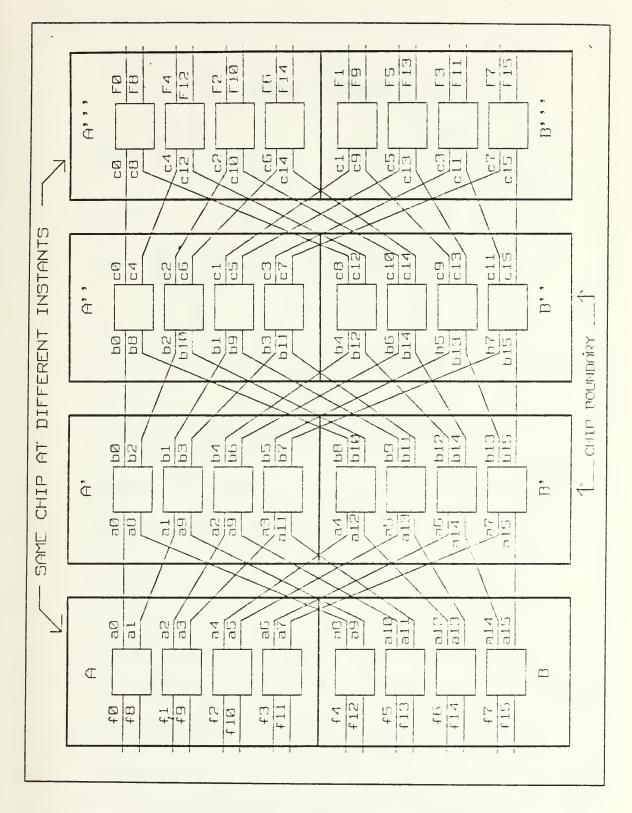

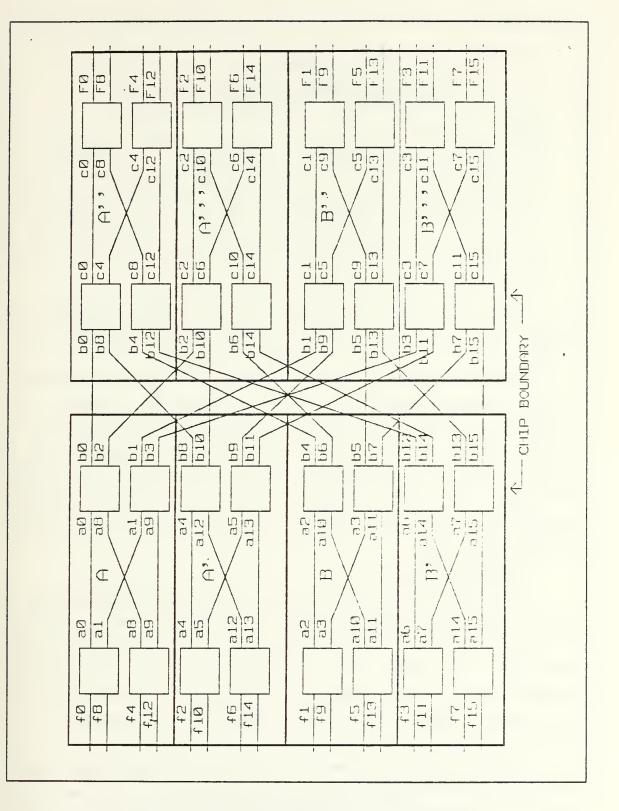

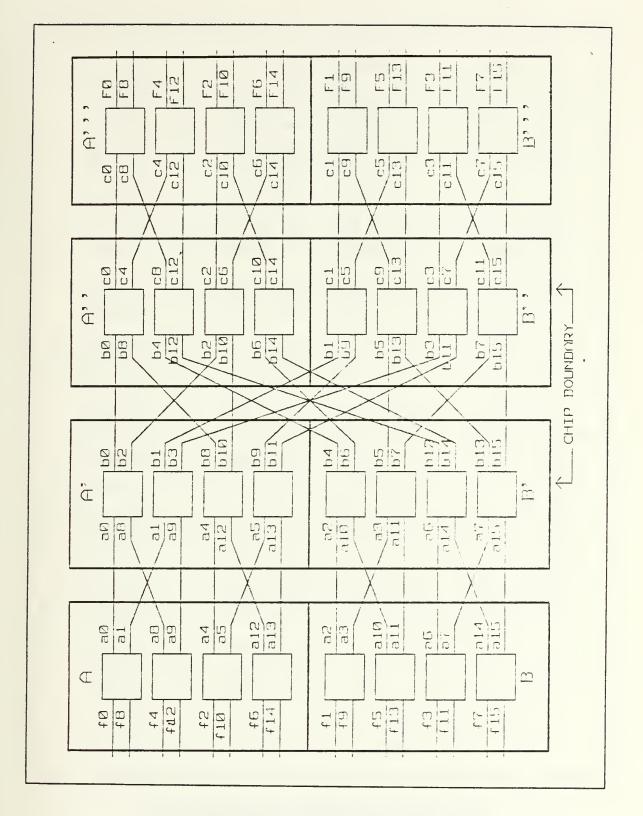

The computations shown in Figure 4.2 still must be performed, but now instead of each block representing an actual processor, it represents a job that some processor will have to perform. For example, consider a 16-point FFT performed with two 4-processor ICs. Figure 4.5 shows the data exchange for this example if the four-processor ICs are organized as  $4 \times 1$  vectors.

As shown in Table V, even though a chip processes eight points every frame, it only transmits four points per frame--keeping half its data onboard for further processing with the half it will receive from the other IC. This assumes that some on-chip communication path exists to enable processors to exchange data.

Figure 4.1 Sixteen Point Fast Fourier Transform [Ref. 3 pp. 2019-22].

Figure 4.2 Sixteen Point Fast Fourier Transform Pipline Implementation.

Figure 4.3 Sixteen Point Fast Fourier Transform Performed by  $4 \times 1$  Chips.

Figure 4.4 Sixteen Point Fast Fourier Transform Performed by 2 × 2 Chips.

Figure 4.5 Sixteen Point Fast Fourier Transform  $4 \times 1$  Reuse Architecture.

| TABLE V                                                    |                                 |          |             |                    |            |                   |            |            |           |            |                  |            |            |           |             |            |

|------------------------------------------------------------|---------------------------------|----------|-------------|--------------------|------------|-------------------|------------|------------|-----------|------------|------------------|------------|------------|-----------|-------------|------------|

| INTER-PROCESSOR COMMUNICATIONS<br>4 X 1 REUSE ARCHITECTURE |                                 |          |             |                    |            |                   |            |            |           |            |                  |            |            |           |             |            |

| Stag<br>#                                                  | Stage Receives Chip A Transmits |          |             |                    |            |                   |            | ]          | Rece      | ives       | B                | Transmits  |            |           |             |            |

|                                                            | 0<br>1                          | f8<br>f9 | f2<br>f3    | f <b>10</b><br>f11 | a <b>1</b> | a <b>5</b>        | a <b>6</b> | a <b>7</b> | f4<br>f6  | f12<br>f14 | f <b>5</b><br>f7 | f13<br>f15 | a <b>s</b> | a 9       | a <b>10</b> | a11        |

| 2 a                                                        | 18                              | a 9      | a <b>10</b> | a11                | b4         | b <b>5</b>        | b6         | b <b>7</b> | <b>a4</b> | а <b>5</b> | a6               | a <b>7</b> | b <b>s</b> | b9        | b10         | b11        |

| 3 b                                                        | 8                               | b9       | b10         | b11                | C1         | С3                | C <b>5</b> | С7         | b4        | b <b>5</b> | b6               | b7         | C8         | C10       | C12         | C14        |

| 4 c                                                        | 8                               | C10      | C12         | C14                | Fo<br>F2   | F <b>8</b><br>F10 | F4<br>F6   | F12<br>F14 | Cl        | С3         | C5               | С7         | F1<br>F5   | F9<br>F13 | F3<br>F7    | F11<br>F15 |

|                                      | -  |     | Ι   | NTE | R-PF<br>2 X | ROCI<br>2 Re | ESS      | ABLE<br>or c<br>e ar      | OM | MUN<br>TEC | VIC<br>TUF | ATIO<br>Re | NS       |           |          |            |

|--------------------------------------|----|-----|-----|-----|-------------|--------------|----------|---------------------------|----|------------|------------|------------|----------|-----------|----------|------------|

| Stage Chip A<br># Receives Transmits |    |     |     |     |             |              |          | Chip B<br>Receives Transi |    |            |            |            |          | smit      | S        |            |

| 1                                    | fo | fø  | f4  | f12 |             |              |          |                           | fı | f9         | f <b>5</b> | f13        |          |           |          |            |

| 2                                    | fz | f10 | f6  | f14 | bı          | bз           | b9       | b11                       | ſз | f11        | f7         | f15        | b4       | b12       | b6       | b14        |

| 3                                    | b4 | b6  | b12 | b14 | Fo<br>F2    | F8<br>F10    | F4<br>F6 | F12<br>F14                | bı | bз         | b9         | b11        | F1<br>F5 | F9<br>F13 | F3<br>F7 | F11<br>F15 |

As an alternative, consider the same 16-point FFT computed by two 4-processor ICs, this time organized as  $2 \times 2$  matrices, as shown in Figure 4.6 and Table VI.

Because each IC is only two processors "wide," a single IC can only accept four data points at a time. This creates an awkward data flow--the source delivers only half the input vector, waits, then delivers the other half. Each chip must store the output of its first computation while processing the second half of the input vector. However, the number of data points exchanged between chips is sharply reduced from 24 for the  $4 \times 1$  case to 8 for the  $2 \times 2$  case.

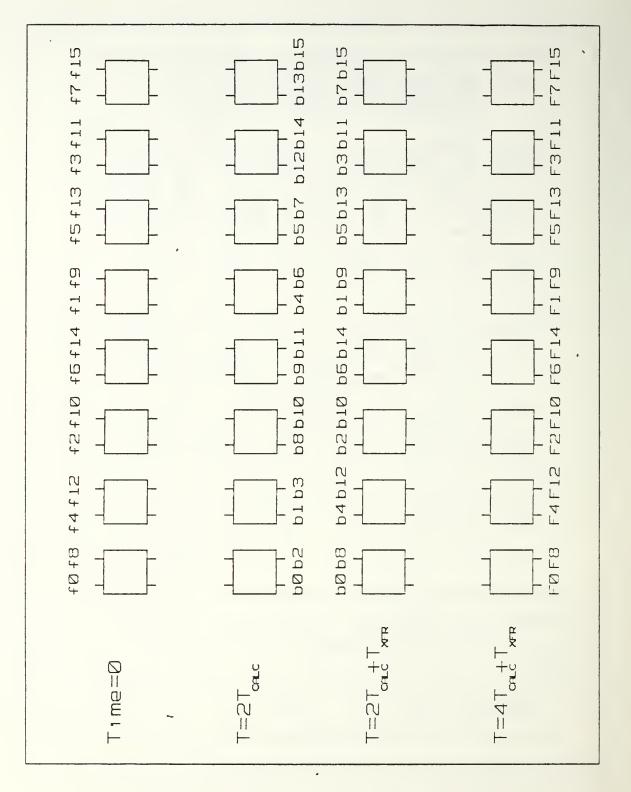

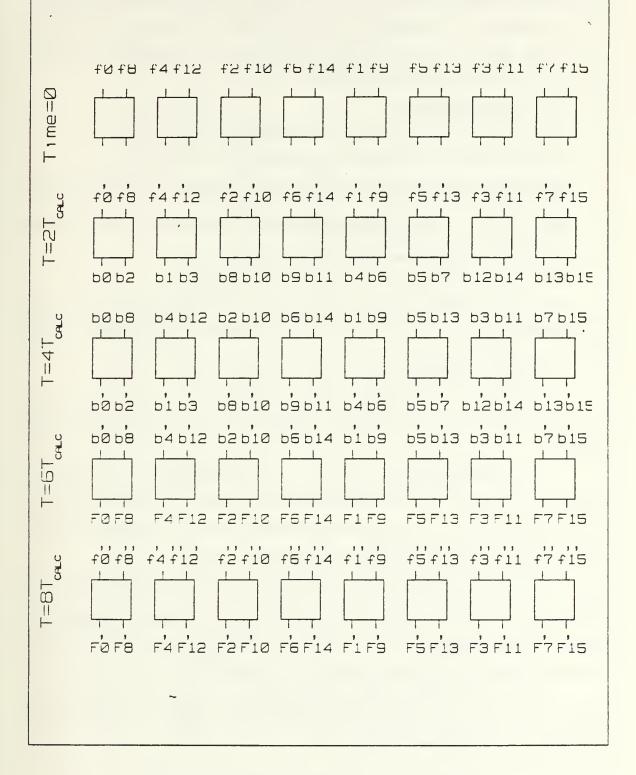

Figure 4.6 Sixteen Point Fast Fourier Transform 2 × 2 Reuse Architecture.